Nachrichten

AMD beginnt mit der Treiberunterstützung für RDNA 3.5 „GFX1151“-GPUs für High-End-Strix-Halo-APUs

AMD hat mit der Einführung der Treiberunterstützung für seine RDNA 3.5 „GFX1151“-GPU begonnen, die in den Premium-Strix-Halo-APUs für Notebooks zum Einsatz kommen wird.

Die leistungsstarken Strix Point Halo APUs von AMD erhalten jetzt Unterstützung für die GPU-Aktivierung mit RDNA 3.5 „GFX1151“.

AMDs Strix-APUs der nächsten Generation werden in zwei Varianten erhältlich sein: einer monolithischen und einer Chiplet-Variante. Beide Chips werden voraussichtlich über die verfeinerten integrierten RDNA 3.5-GPUs verfügen, wobei der Mono-Chip ein GFX 1150-Design (16 CU) und die Chiplet-Variante ein GFX1151-Design (40 CU) haben wird. Wir haben gesehen, dass das Unternehmen vor einiger Zeit mit der Unterstützung der Mono-Variante (GFX 1150) begonnen hat, und jetzt beginnt das rote Team mit der Aktivierung des High-End-Chips.

Im MESA 24.1-Update für die RadeonSI/RADV-Treiber haben AMD-Ingenieure den entsprechenden Code zur Aktivierung der GFX1151-IP hinzugefügt, was bedeutet, dass die Vorarbeiten für die High-End-Strix-APUs begonnen haben.

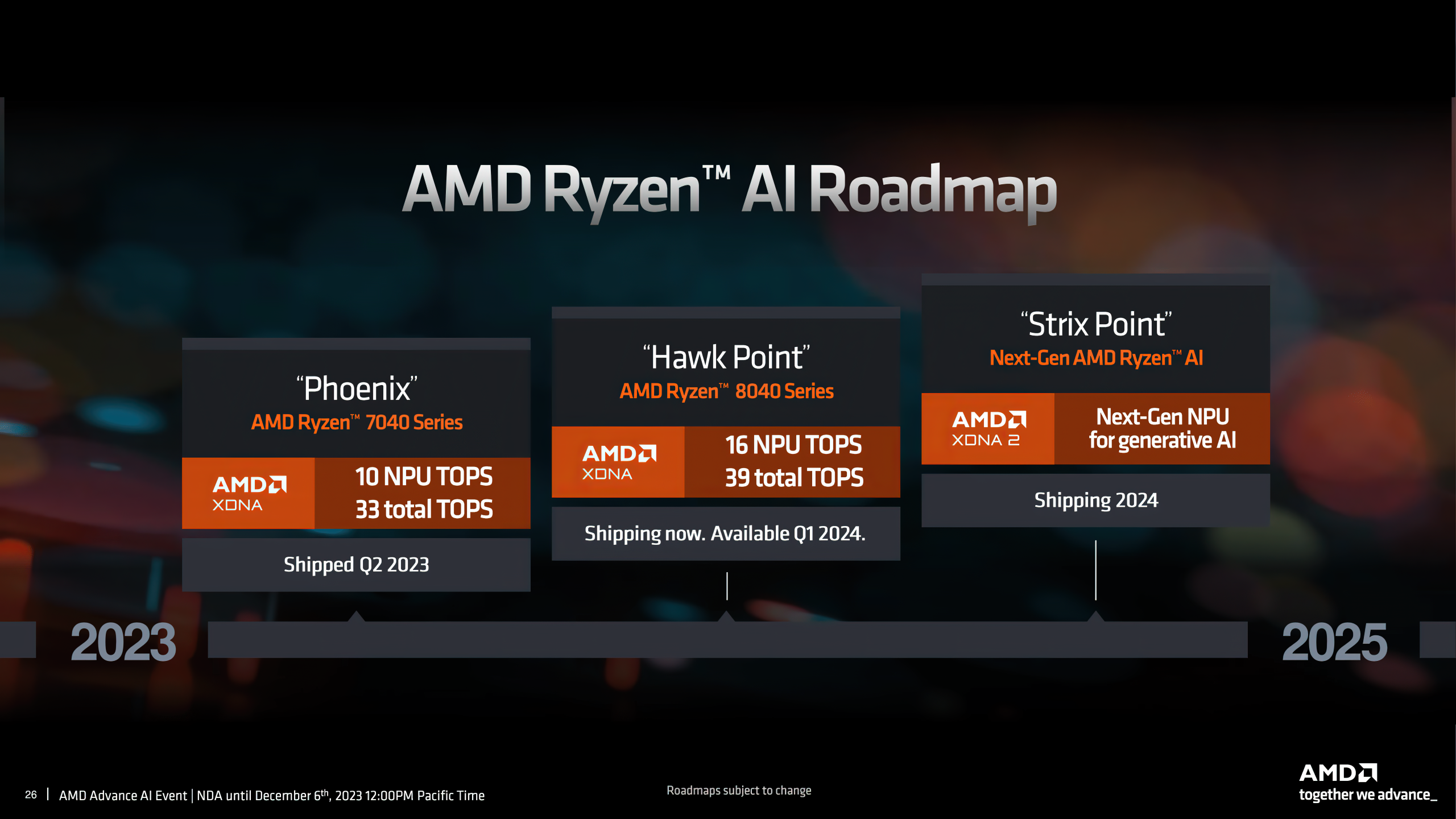

Der Code selbst enthält nicht viele Informationen, aber AMD Strix APUs werden voraussichtlich einen großen Sprung gegenüber den Hawk Point APUs darstellen, die größtenteils eine Aktualisierung der Phoenix-Chips waren, die auf den Zen 4-CPU- und RDNA 3-GPU-Architekturen basierten. In der Zwischenzeit wird Strix neuere Zen 5-Kerne und die neuesten RDNA 3.5-GPU-Kerne integrieren, von denen eine bessere Leistung und eine bessere APU-Effizienz erwartet wird.

Erwartete Funktionen des AMD Ryzen 8050 Strix Point Mono:

- Zen 5 (4 nm) Monolithisches Design

- Bis zu 12 Kerne in Hybridkonfiguration (Zen 5 + Zen 5C)

- 32 MB gemeinsam genutzter L3-Cache

- 16 RDNA 3+ Recheneinheiten

- 128-Bit LPDDR5X-Speichercontroller

- XDNA 2 Engine integriert

- ~25 TOPS KI-Engine

- Start im 2. Halbjahr 2024 (erwartet)

Erwartete Funktionen des AMD Ryzen 8050 Strix Point Halo:

- Zen 5 Chiplet-Design

- Bis zu 16 Kerne

- 64 MB gemeinsam genutzter L3-Cache

- 40 RDNA 3+ Recheneinheiten

- 256-Bit-LPDDR5X-Speichercontroller

- XDNA 2 Engine integriert

- ~50 TOPS KI-Engine

- Start im 2. Halbjahr 2024 (erwartet)

Die AMD Strix Point APUs werden voraussichtlich in der zweiten Hälfte des Jahres 2024 auf den Markt kommen, wobei die ersten APU-Auslieferungen an OEMs im nächsten Jahr beginnen. Dies wird ungefähr zur gleichen Zeit sein, in der Intel seine Arrow-Lake- und Lunar-Lake-CPUs anbieten wird, den Nachfolger von Meteor Lake.

Nachrichtenquelle: Phoronix