Nachrichten

AMDs Zen 5 EPYC „Turin“-CPUs der nächsten Generation im Bild: Leak enthüllt 128 Core Zen 5- und 192 Core Zen 5C-Varianten

AMDs EPYC Turin-CPUs der nächsten Generation mit Zen 5- und Zen 5C-Architektur in 128-Kern- und 192-Kern-Konfigurationen sind durchgesickert.

AMD EPYC Turin-CPUs der 5. Generation sind durchgesickert: Die Konfigurationen im Detail mit bis zu 128 Core Zen 5- und 192 Core Zen 5C-Konfigurationen

Das neueste Leck stammt von YuuKi_AnS der nicht nur die ersten technischen Muster der AMD EPYC Turin-CPUs der nächsten Generation durchgesickert hat, sondern auch die Chip-Konfigurationen vorgestellt hat, die wir mit diesen Hochleistungs-Serverchips erwarten können.

Was die Details angeht: Der AMD EPYC Turin wird die EPYC-Reihe der 5. Generation sein, die die EPYC-Familie der 4. Generation ersetzt. Die EPYC-Familie der 4. Generation besteht aus Genoa-, Genoa-X-, Bergamo- und Siena-CPUs, die Zen 4- und Zen 4C-Kerne in EPYC 9004/8004-SKUs verwenden. Die EPYC-Familie der 5. Generation wird ähnlich sein und eine Reihe von Konfigurationen und SKUs mit Zen 5 „Nirvana“- und Zen 5C „Prometheus“-Kernen umfassen. Es wird erwartet, dass die Zen 5-Kerne den 3-nm-Prozessknoten nutzen, während der Zen 5C möglicherweise die gleiche oder eine optimierte Variante nutzt.

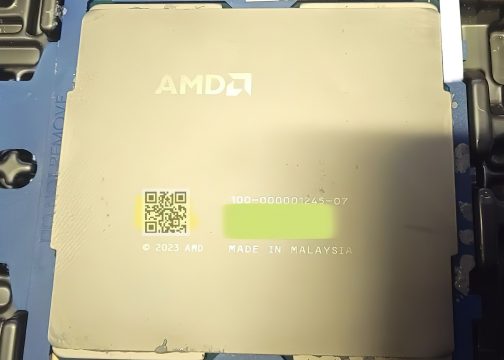

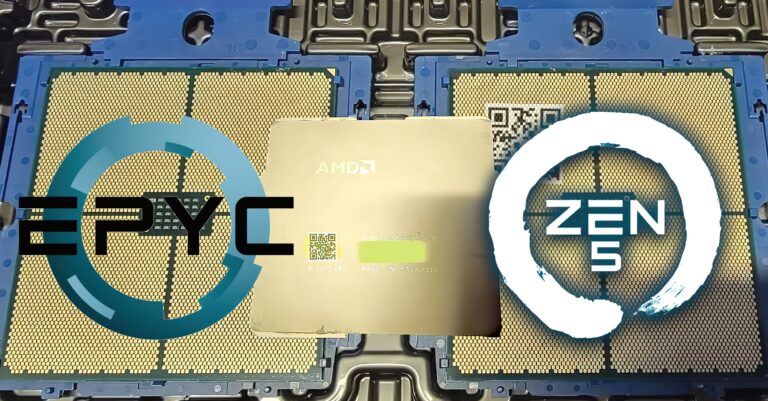

Basierend auf den durchgesickerten Bildern handelt es sich um einen AMD EPYC „Turin“ ES2-Chip mit dem OPN-Code 100-000001245-07. Dieser Chip wurde im Jahr 2023 hergestellt und scheint sehr neu zu sein. Die Trägerhalterung für AMD Zen 5 Turin-Classic-Chips scheint hellblau zu sein und diese Chips sollten die Sockelkompatibilität mit der SP5-Plattform beibehalten, die für High-End-Chips konzipiert ist. Es bietet derzeit Unterstützung für die oben genannte EPYC 9004-Reihe.

Es sollte darauf hingewiesen werden, dass vor einigen Monaten derselbe OPN-Code erwähnt wurde Dito_55. Der Benutzer listete auch verschiedene andere Konfigurationen für die CPU-Familie AMD EPYC Turin (intern Codename Breithorn) auf, darunter:

- 100-000001245 – 16 CCD + 1 IOD (128 Zen 5 Core / 256 Thread / 512 MB Cache)

- 100-000001341 – 12 CCD + 1 IOD (96 Zen 5 Kerne / 192 Threads / 384 MB Cache)

- 100-000001247 – 8 CCD + 1 IOD (64 Zen 5 Kerne / 128 Threads / 256 MB Cache)

- 100-000001342 – 8 CCD + 1 IOD (64 Zen 5 Kerne / 128 Threads / 256 MB Cache)

- 100-000001249 – 2 CCD + 1 IOD (32 Zen 5C-Kerne / 64 Threads / 64 MB Cache)

AMD EPYC Turin-CPUs der 5. Generation mit Zen 5 Classic-Architektur – bis zu 128 Kerne

Beginnend mit den Konfigurationen bieten die AMD EPYC Turin-CPUs mit Zen 5 Classic-Kernen bis zu 128 Kerne und 256 Threads. Es wird maximal 16 CCDs mit jeweils 8 Kernen geben, und jeder CCD wird über einen eigenen 32 MB L3-Cache verfügen. Dadurch werden bis zu 512 MB L3-Cache gebildet. Dies bedeutet eine Steigerung der Kernanzahl um 33 Prozent und der gesamten L3-Cache-Anzahl um 33 Prozent im Vergleich zur Zen 4-basierten EPYC Genoa-Familie.

Das IOD wird neben einer Liste weiterer Controller und Beschleuniger über einen integrierten DDR5-Speichercontroller mit Unterstützung für Geschwindigkeiten von 6000 MT/s sowie PCIe Gen5 (CXL 2.0), Gen3 Infinity Fabric und Secure Processor-Unterstützung verfügen.

AMD EPYC Turin-CPUs der 5. Generation mit Zen 5C Dense-Architektur – bis zu 192 Kerne

Bei der AMD EPYC Turin-CPU mit den Zen 5C-Kernen geht es richtig krachend zu: Jeder Zen 5C CCD bietet bis zu 16 Kerne und 32 MB L3-Cache. An Bord dieser Chips werden sechs Rechenchiplets für insgesamt 192 Kerne und 256 Threads mit leicht reduzierten 384 MB L3-Cache sein. Die CPUs behalten die gleichen I/Os wie die anderen klassischen Chips.

Im Vergleich zu AMDs EPYC Bergamo-CPUs, die auf den Zen 4C-Kernen basieren, bieten die Turin-Chips mit Zen 5C-Kernen eine 50-prozentige Steigerung der Anzahl der Kerne und Threads (192/384 gegenüber 128/256) und bieten gleichzeitig die gleiche Steigerung von 50 %. in der gesamten Cache-Anzahl (384 MB vs. 256 MB). Sowohl die Zen 5- als auch die Zen 5C-Chips werden voraussichtlich über eine TDP von 480 W verfügen, die auf bis zu 600 W konfiguriert werden kann. Die Erhöhung der Rechenkapazitäten wird einen schrittweisen Weg zu bestehenden Servern markieren, die diese Chips einfach in bestehende Plattformen einbauen und den zusätzlichen Boost genießen können.

AMD hat bisher bestätigt, dass die EPYC Turin-CPUs auf Basis der Zen-5-Kernarchitektur auf dem Weg zur Markteinführung im Jahr 2024 sind und einen deutlichen Leistungssprung pro Watt liefern werden. Die zusätzliche Kernzahl und die verbesserte Architektur dürften AMD dabei helfen, eine starke und wettbewerbsfähige Lösung gegenüber den Granite Rapids Xeon-Chips von Intel zu liefern, deren Einführung ebenfalls im kommenden Jahr erwartet wird.

AMD EPYC CPU-Familien:

| Familienname | AMD EPYC Venedig | AMD EPYC Turin-Dense | AMD EPYC Turin-X | AMD EPYC Turin | AMD EPYC Siena | AMD EPYC Bergamo | AMD EPYC Genua-X | AMD EPYC Genua | AMD EPYC Milan-X | AMD EPYC Mailand | AMD EPYC Rom | AMD EPYC Neapel |

|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Familienbranding | EPYC 11K? | EPYC 10K? | EPYC 10K? | EPYC 10K? | EPYC 8004 | EPYC 9004 | EPYC 9004 | EPYC 9004 | EPYC 7004 | EPYC 7003 | EPYC 7002 | EPYC 7001 |

| Familienstart | 2025+ | 2025? | 2025? | 2024 | 2023 | 2023 | 2023 | 2022 | 2022 | 2021 | 2019 | 2017 |

| CPU-Architektur | Zen 6? | Zen 5C | Zen 5 | Zen 5 | Zen 4 | Zen 4C | Zen 4 V-Cache | Zen 4 | Zen 3 | Zen 3 | Zen 2 | Zen 1 |

| Prozessknoten | Noch offen | 3 nm TSMC? | 4 nm TSMC | 4 nm TSMC | 5 nm TSMC | 4 nm TSMC | 5 nm TSMC | 5 nm TSMC | 7 nm TSMC | 7 nm TSMC | 7 nm TSMC | 14 nm GloFo |

| Plattformname | Noch offen | SP5 | SP5 | SP5 | SP6 | SP5 | SP5 | SP5 | SP3 | SP3 | SP3 | SP3 |

| Steckdose | Noch offen | LGA 6096 (SP5) | LGA 6096 (SP5) | LGA 6096 | LGA 4844 | LGA 6096 | LGA 6096 | LGA 6096 | LGA 4094 | LGA 4094 | LGA 4094 | LGA 4094 |

| Maximale Kernanzahl | 384? | 192 | 128 | 128 | 64 | 128 | 96 | 96 | 64 | 64 | 64 | 32 |

| Maximale Threadanzahl | 768? | 384 | 256 | 256 | 128 | 256 | 192 | 192 | 128 | 128 | 128 | 64 |

| Maximaler L3-Cache | Noch offen | 384 MB | 1536 MB | 384 MB | 256 MB | 256 MB | 1152 MB | 384 MB | 768 MB | 256 MB | 256 MB | 64 MB |

| Chiplet-Design | Noch offen | 12 CCDs (1CCX pro CCD) + 1 IOD | 16 CCDs (1CCX pro CCD) + 1 IOD | 16 CCDs (1CCX pro CCD) + 1 IOD | 8 CCDs (1CCX pro CCD) + 1 IOD | 12 CCDs (1 CCX pro CCD) + 1 IOD | 12 CCDs (1 CCX pro CCD) + 1 IOD | 12 CCDs (1 CCX pro CCD) + 1 IOD | 8 CCDs (1 CCX pro CCD) + 1 IOD | 8 CCDs (1 CCX pro CCD) + 1 IOD | 8 CCDs (2 CCXs pro CCD) + 1 IOD | 4 CCDs (2 CCXs pro CCD) |

| Speicherunterstützung | Noch offen | DDR5-6000? | DDR5-6000? | DDR5-6000? | DDR5-5200 | DDR5-5600 | DDR5-4800 | DDR5-4800 | DDR4-3200 | DDR4-3200 | DDR4-3200 | DDR4-2666 |

| Speicherkanäle | Noch offen | 12 Kanäle (SP5) | 12 Kanäle (SP5) | 12 Kanäle | 6-Kanal | 12 Kanäle | 12 Kanäle | 12 Kanäle | 8 Kanäle | 8 Kanäle | 8 Kanäle | 8 Kanäle |

| PCIe-Gen-Unterstützung | Noch offen | Noch offen | Noch offen | Noch offen | 96 Gen 5 | 128 Gen 5 | 128 Gen 5 | 128 Gen 5 | 128 Gen 4 | 128 Gen 4 | 128 Gen 4 | 64 Gen 3 |

| TDP (max.) | Noch offen | 480 W (cTDP 600 W) | 480 W (cTDP 600 W) | 480 W (cTDP 600 W) | 70-225W | 320 W (cTDP 400 W) | 400W | 400W | 280W | 280W | 280W | 200W |